UNIVERSITY OF MALTA

# Runtime Monitoring of Duration Calculus Assertions for Real-Time Applications

by Karlston D'Emanuele

A dissertation submitted in fulfillment of the degree of Masters of Science

Department of Computer Science and A.I. Faculty of Science University of Malta September 2006 Supervisor:

Dr. Gordon Pace

External Examiner: Dr. Raymond Pascal

Other Examiners:

Dr. Kevin Vella Mr. Mike Rosner

"If in other sciences we should arrive at certainty without doubt and truth without errors, it behooves us to place the foundations of knowledge in mathematics."

Roger Bacon English Mathematician (1220–1292) [Opus Majus, bk. 1, ch. 4]

#### Abstract

An open question which is commonly asked in software development is whether the implemented artefact follows the requirements specified. From the early days of computing, a number of projects, ideas and techniques have been proposed to prove software correctness. One of these techniques is validation, which verifies the system during execution.

Duration Calculus is a powerful logic notation that evaluates property satisfaction by applying the Reimann integral over property values within an interval. Therefore, Duration Calculus not only determines whether a property is being satisfied but also the duration of the property satisfiability. Duration Calculus notation considers time as a real valued variable, which together with the evaluation of calculi formulae becomes undecidable. In this dissertation, we restrict the notation to a subset that is decidable, discrete-time and deterministic. The decidability property is important in order to evaluate the system correctness at runtime. On the other hand, the restriction to discrete-time together with the determinism of the notation reduce the side-effects of the inserting observers in the actual system thus guaranteeing the correctness of the verified program.

After restricting Duration Calculus notation to the suitable subset of operators, we propose a framework for defining monitors and integrating them with the system code. Our framework allows monitors to be defined using the mathematical notation, which through a pre-compiler is converted to its Lustre semantics and stored inside Abstract Syntax Trees. The synchronous data-flow programming language Lustre is used for the notation semantics because the resource requirements for the monitors can be predetermined. To keep the benefits obtained by using Lustre, the monitoring platform is also defined in Lustre. The final step before executing the system is to integrate the monitors inside the code. The weaving of monitors with the system is performed through the concept of annotated assertions, which are converted into function calls to the Lustre based evaluation engine to determine the properties satisfiability.

We conclude our research by showing the concept of Interval Temporal Logic validation as an aspect, within the Aspect-Oriented Programming (AOP) framework. This concept can be used to facilitate the design of more robust and flexible validation engine simply by defining notation semantics.

#### Acknowledgements

I would like to express my deepest gratitude to my supervisor Dr. Gordon Pace for his continuous assessments, guidance and knowledge sharing during the entire stages of the dissertation. I also thank him for forwarding the concepts of synchronous programming and Aspect-Oriented Programming that were of major help for the dissertation.

Thanks go to Mr. Joseph Cordina for his assistance in checking the mathematical formulae and for his support. I would also like to thank my colleagues for their support and the good time passed at the University during the research. I take this occasion to thank the Semantics and Verification Research Group for their useful comments and knowledge sharing. I am grateful to the Department of Computer Science and Artificial Intelligence for providing the necessary space and facilities to perform this dissertation with the least inconveniences as possible.

My greatest gratitude goes to my parents who have always given their support and help whenever was possible. I also thank my brother who although not well literate on the subject has shared his ideas and for proof reading the dissertation from the grammatical side. Finally but not least I would like to thank my friends for their support and help throughout the dissertation.

# Contents

| A             | bstra | ict                                        | i    |

|---------------|-------|--------------------------------------------|------|

| $\mathbf{A}$  | cknov | wledgements                                | ii   |

| C             | onter | nts                                        | iii  |

| Li            | st of | Tables                                     | viii |

| $\mathbf{Li}$ | st of | Figures                                    | ix   |

| 1             | Intr  | roduction                                  | 1    |

|               | 1.1   | Objectives                                 | 3    |

|               | 1.2   | Report Layout                              | 5    |

| Ι             | Ba    | ckground                                   | 6    |

| <b>2</b>      | Dur   | ration Calculus                            | 7    |

|               | 2.1   | Duration Calculus Syntax and Semantics     | 7    |

|               |       | 2.1.1 Duration Calculus examples           | 15   |

|               | 2.2   | Quantified Discrete-time Duration Calculus | 15   |

|               |       | 2.2.1 QDDC syntax and semantics            | 15   |

|   |      | 2.2.2 QDDC examples                                             | 20        |

|---|------|-----------------------------------------------------------------|-----------|

|   | 2.3  | Conclusion                                                      | 20        |

| 3 | Vali | dation                                                          | 21        |

|   | 3.1  | Assertions                                                      | 21        |

|   |      | 3.1.1 Atemporal assertions                                      | 22        |

|   |      | 3.1.2 Temporal logic assertions                                 | 24        |

|   |      | 3.1.3 Interval temporal logic                                   | 26        |

|   | 3.2  | Related projects                                                | 27        |

|   |      | 3.2.1 EAGLE Flier                                               | 27        |

|   |      | 3.2.2 Java-MaC                                                  | 28        |

|   |      | 3.2.3 Temporal Rover                                            | 30        |

|   |      | 3.2.4 RTMAssertions                                             | 32        |

|   |      | 3.2.5 Other projects                                            | 34        |

|   | 3.3  | Monitoring-Oriented Programming                                 | 37        |

|   |      |                                                                 |           |

| Π | Di   | screte and Deterministic subset of Duration Calculus Assertions | <b>40</b> |

| 4 | QD   | DC to Symbolic Automata                                         | 41        |

|   | ·    |                                                                 |           |

|   | 4.1  | Deterministic QDDC                                              | 42        |

|   | 4.2  | Lustre environment                                              | 45        |

|   | 4.3  | Helper functions                                                | 47        |

|   | 4.4  | Deterministic QDDC Operators Semantics                          | 49        |

|   | 4.5  | Conclusion                                                      | 50        |

### 5 Validation Engine

|   | 5.1 | Symbo             | olic Automata Initialisation                         | 51 |

|---|-----|-------------------|------------------------------------------------------|----|

|   |     | 5.1.1             | Space complexity                                     | 52 |

|   | 5.2 | Evalua            | ation Process                                        | 53 |

|   |     | 5.2.1             | Time complexity                                      | 55 |

|   | 5.3 | Valida            | tion Process                                         | 55 |

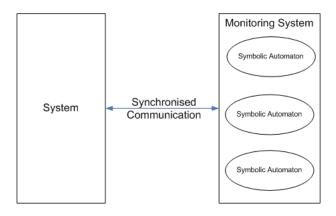

|   |     | 5.3.1             | Monitoring System                                    | 56 |

|   |     | 5.3.2             | Interface                                            | 57 |

|   | 5.4 | Conclu            | usion                                                | 58 |

| 0 | ъ   |                   | (D <sup>3</sup> C)                                   | 50 |

| 6 | Pro | totype            | $\mathbf{P}$ of $\mathbf{D}^{3}\mathbf{C}\mathbf{A}$ | 59 |

|   |     | 6.0.1             | Getting to AST                                       | 59 |

|   | 6.1 | D <sup>3</sup> CA | - C++                                                | 61 |

|   |     | 6.1.1             | Lustre Environment                                   | 61 |

|   |     | 6.1.2             | Initialising                                         | 62 |

|   |     | 6.1.3             | Validation Engine                                    | 62 |

|   |     | 6.1.4             | Analysis                                             | 63 |

|   | 6.2 | $\# D^{3}C$       | Α                                                    | 63 |

|   |     | 6.2.1             | Weaver                                               | 63 |

|   |     | 6.2.2             | Annotations                                          | 65 |

|   |     | 6.2.3             | Lustre environment                                   | 66 |

|   |     | 6.2.4             | Validation Engine                                    | 67 |

|   | 6.3 | Analys            | sis                                                  | 67 |

51

### 7 Case Studies

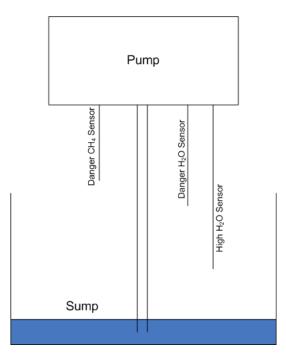

|          | 7.1                                                                                      | Mine Pump                                                                                                                                                                                                                                                   |                                                                                                            |  |  |

|----------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|

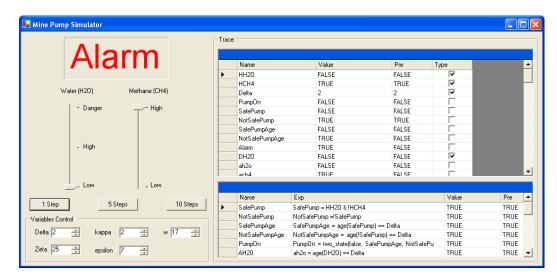

|          | 7.2                                                                                      | QDDC Specifications                                                                                                                                                                                                                                         | 70                                                                                                         |  |  |

|          |                                                                                          | 7.2.1 Creating the validation engine                                                                                                                                                                                                                        | 72                                                                                                         |  |  |

|          |                                                                                          | 7.2.2 Simple Test Scenario                                                                                                                                                                                                                                  | 72                                                                                                         |  |  |

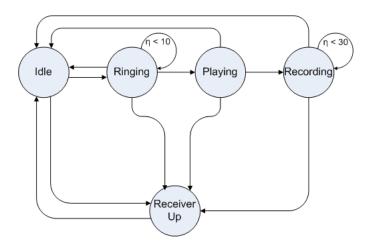

|          | 7.3                                                                                      | A Simple Answering Machine                                                                                                                                                                                                                                  | 73                                                                                                         |  |  |

|          |                                                                                          | 7.3.1 QDDC Specifications                                                                                                                                                                                                                                   | 74                                                                                                         |  |  |

|          | 7.4                                                                                      | Creating the validation engine                                                                                                                                                                                                                              | 75                                                                                                         |  |  |

|          | 7.5                                                                                      | Simple Test Scenarios                                                                                                                                                                                                                                       | 76                                                                                                         |  |  |

|          | 7.6                                                                                      | Conclusion                                                                                                                                                                                                                                                  | 79                                                                                                         |  |  |

|          |                                                                                          |                                                                                                                                                                                                                                                             |                                                                                                            |  |  |

|          |                                                                                          |                                                                                                                                                                                                                                                             |                                                                                                            |  |  |

| II       | ΙV                                                                                       | alidation and Aspect-Oriented Programming                                                                                                                                                                                                                   | 80                                                                                                         |  |  |

| II.<br>8 |                                                                                          | Validation and Aspect-Oriented Programming                                                                                                                                                                                                                  | 80<br>81                                                                                                   |  |  |

|          |                                                                                          |                                                                                                                                                                                                                                                             |                                                                                                            |  |  |

|          | $\mathbf{ITL}$                                                                           | validation as an aspect                                                                                                                                                                                                                                     | 81                                                                                                         |  |  |

|          | <b>ITL</b><br>8.1                                                                        | validation as an aspect         Validation as an Aspect                                                                                                                                                                                                     | <b>81</b><br>82                                                                                            |  |  |

|          | <b>ITL</b><br>8.1<br>8.2<br>8.3                                                          | validation as an aspect         Validation as an Aspect         Defining D <sup>3</sup> CA weaver in AOP terms                                                                                                                                              | <b>81</b><br>82<br>84                                                                                      |  |  |

| 8        | <b>ITL</b><br>8.1<br>8.2<br>8.3                                                          | validation as an aspect         Validation as an Aspect         Defining D <sup>3</sup> CA weaver in AOP terms         Conclusion                                                                                                                           | <b>81</b><br>82<br>84<br>85                                                                                |  |  |

| 8        | <ul><li>ITL</li><li>8.1</li><li>8.2</li><li>8.3</li><li>Con</li></ul>                    | validation as an aspect         Validation as an Aspect         Defining D <sup>3</sup> CA weaver in AOP terms         Conclusion         Conclusion                                                                                                        | <ul><li>81</li><li>82</li><li>84</li><li>85</li><li>86</li></ul>                                           |  |  |

| 8        | <ul><li>ITL</li><li>8.1</li><li>8.2</li><li>8.3</li><li>Con</li></ul>                    | validation as an aspect         Validation as an Aspect         Defining D <sup>3</sup> CA weaver in AOP terms         Conclusion         Conclusion         Research Overview                                                                              | <ul> <li>81</li> <li>82</li> <li>84</li> <li>85</li> <li>86</li> <li>87</li> </ul>                         |  |  |

| 8        | <ul> <li>ITL</li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>Con</li> <li>9.1</li> </ul> | validation as an aspect         Validation as an Aspect         Defining D <sup>3</sup> CA weaver in AOP terms         Conclusion         Conclusion         Research Overview         9.1.1         Monitoring System         Possible future enhancements | <ul> <li>81</li> <li>82</li> <li>84</li> <li>85</li> <li>86</li> <li>87</li> <li>87</li> <li>88</li> </ul> |  |  |

| 8        | <ul> <li>ITL</li> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>Con</li> <li>9.1</li> </ul> | validation as an aspect         Validation as an Aspect         Defining D <sup>3</sup> CA weaver in AOP terms         Conclusion         Conclusion         Research Overview         9.1.1         Monitoring System                                      | <ul> <li>81</li> <li>82</li> <li>84</li> <li>85</li> <li>86</li> <li>87</li> <li>87</li> </ul>             |  |  |

69

|    | 9.3 Summary                           | 90 |

|----|---------------------------------------|----|

| A  | "leads to" operator in terms of age() | 91 |

| в  | Case Studies Properties in XML format | 92 |

|    | B.1 Mine Pump                         | 92 |

|    | B.2 Answering Machine                 | 95 |

| Bi | bliography                            | 98 |

# List of Tables

| 3.1 | Assertion Classification    | 22 |

|-----|-----------------------------|----|

| 3.2 | Eagle vs. $D^3CA$           | 28 |

| 3.3 | MaC vs. $D^3CA$             | 30 |

| 3.4 | Temporal Rover vs. $D^3CA$  | 31 |

| 3.5 | RTMAssertions vs. $D^{3}CA$ | 34 |

# List of Figures

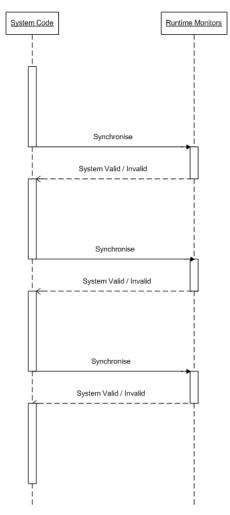

| 1.1 | Abstracted view of monitors evaluation during program execution   | 2  |

|-----|-------------------------------------------------------------------|----|

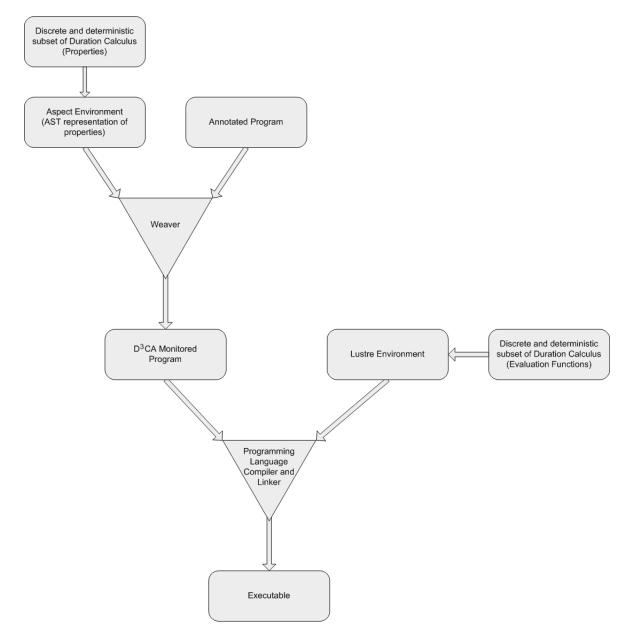

| 1.2 | Overview diagram of dissertation work.                            | 4  |

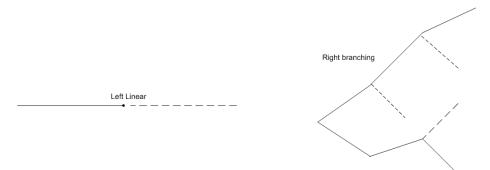

| 3.1 | Linear and branching temporal logic diagram                       | 25 |

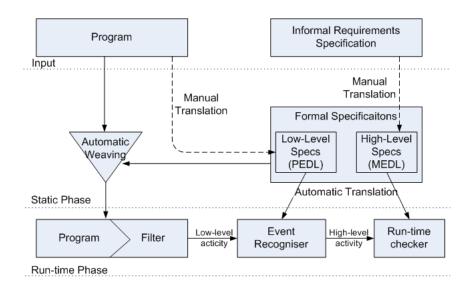

| 3.2 | Overview of the MaC architecture.                                 | 29 |

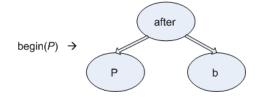

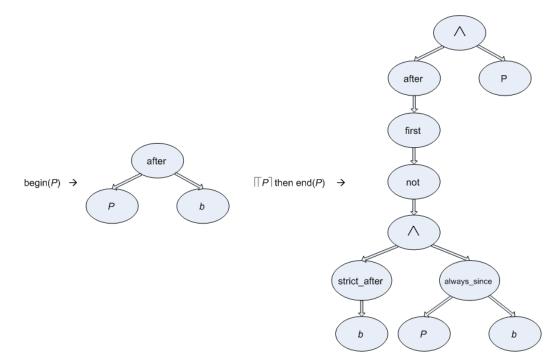

| 3.3 | Evaluation decomposition of $begin(P)$                            | 33 |

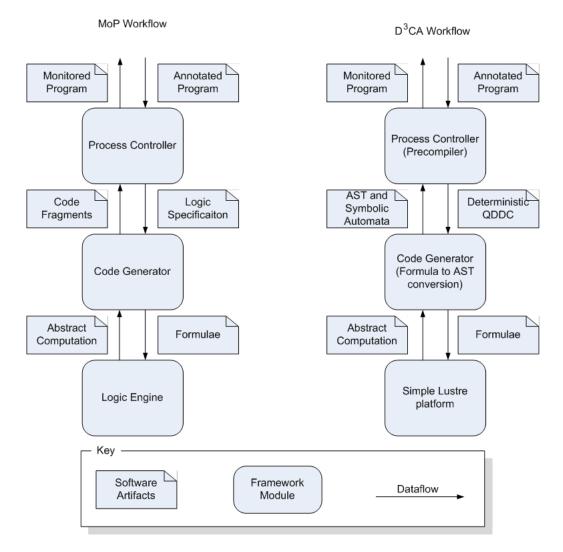

| 3.4 | MoP and $D^3CA$ workflow comparison.                              | 38 |

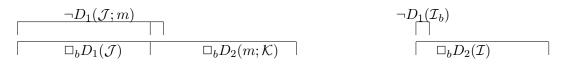

| 4.1 | Block diagram for then operator                                   | 43 |

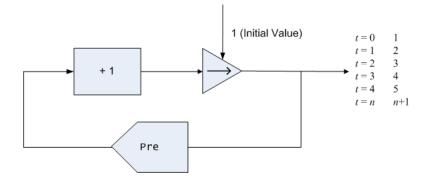

| 4.2 | Counter example in Lustre with variable initialisation            | 47 |

| 5.1 | Abstracted view of the validation engine.                         | 52 |

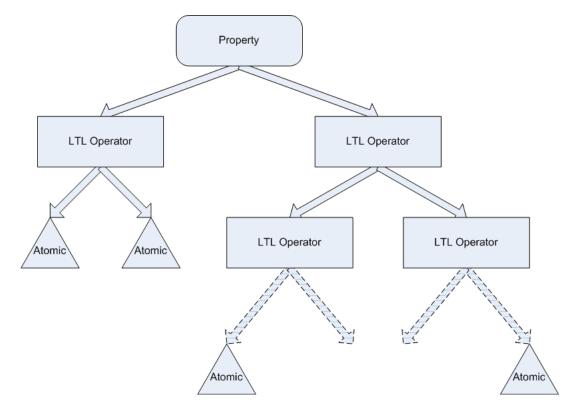

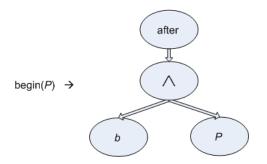

| 5.2 | Evaluation decomposition of $begin(P)$                            | 52 |

| 5.3 | AST representation of $begin(P)$                                  | 53 |

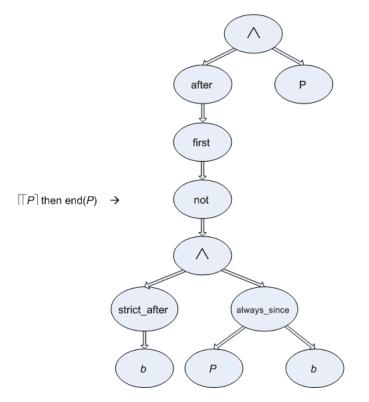

| 5.4 | $\llbracket P  ceil$ then end(P) – Evaluation tree representation | 54 |

| 5.5 | System composition diagram                                        | 55 |

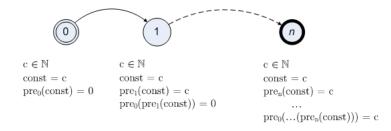

| 5.6 | Lustre constant to system state relation                          | 56 |

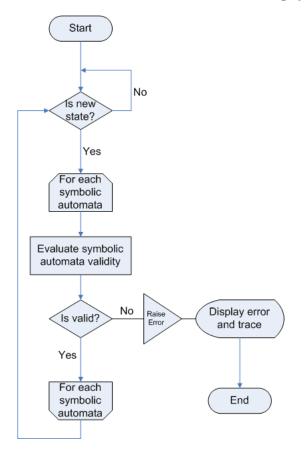

| 5.7 | Validation process flowchart                                      | 57 |

| 5.8 | Sequence diagram for synchronise.                                 | 58 |

| 6.1 | AST representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.2 | $D^{3}CA$ Architecture Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64 |

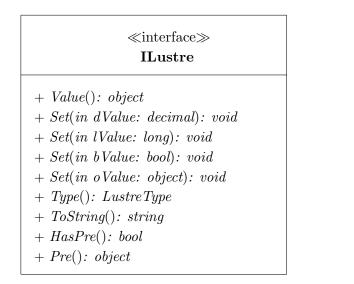

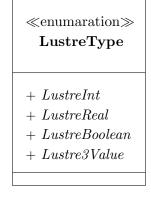

| 6.3 | $\# D^3 CA$ Lustre Interface and Enumeration UML Diagram $\hdots \hdots $ | 66 |

| 7.1 | Mine Pump Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70 |

| 7.2 | Mine Pump Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72 |

| 7.3 | Answering Machine State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

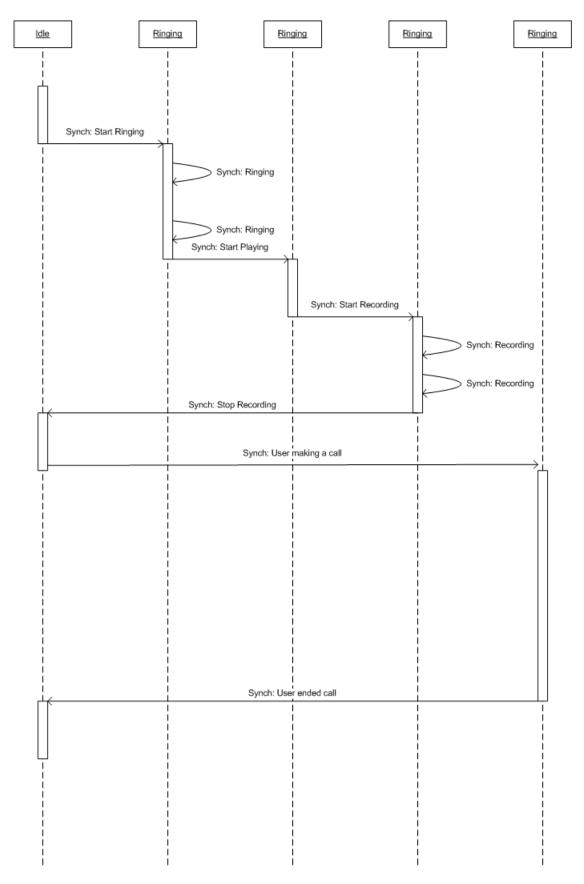

| 7.4 | A Simple Answering Machine – Sequence Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77 |

| 7.5 | Answering Machine Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78 |

| 7.6 | Answering Machine Simulation – Error Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78 |

| 8.1 | Aspect-Oriented Programming Architecture Overview.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82 |

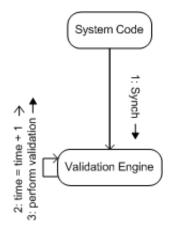

| 8.2 | Synchronise communication diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83 |

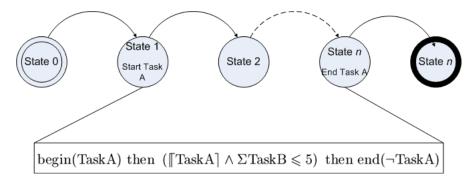

| 8.3 | States representing an execution path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83 |

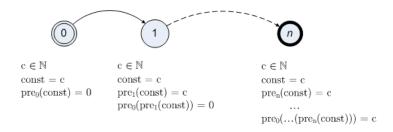

| 8.4 | Lustre constant to system state relation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85 |

| 9.1 | Multiple Validation Interfaces Architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 89 |

### Chapter 1

### Introduction

"...unexpected behavior, by definition, violates an application's formal specification, the specification casts a wide net for catching software exceptions, exceptions that you might miss. Therefore, using formal specifications to generate exception handling routines produces a robust hybrid program having multiple levels of recovery paths. The additional levels shield the application from worst-case scenarios that would otherwise crash it."

Doron Drusinsky [Dru01]

A common question that arises during software development is whether the system being implemented is correct according to the given specifications. With the complexities reachable today in software development, guaranteeing correctness of the software is becoming more intractable. Over the past years a number of projects have been commenced in order to propose possible solutions to manage and control software correctness.

From the many projects and ideas proposed in other papers, a solution which is of prime interest to us is about executing runtime monitors in parallel to software code. Runtime monitors can be of different nature ranging from simple propositional statements inserted as conditional checks to the use of temporal logic based automata. Runtime monitors verify the software along its execution path, thus they only guarantee the correctness of the system along a single path. Although this is a drawback of the approach it pays off in resource requirements when compared to the more elaborate process of formal verification. Formal verification consists in performing logical inference over the system specifications to determine their correctness.

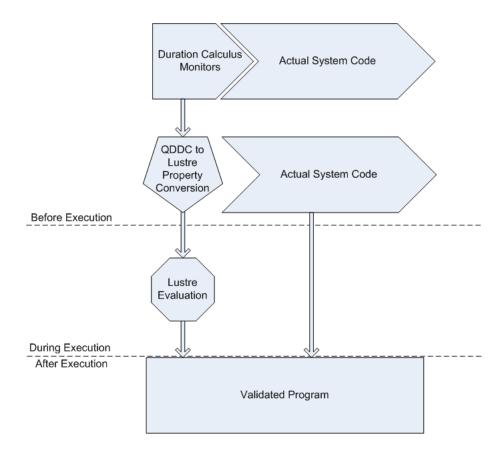

Figure 1.1: Abstracted view of monitors evaluation during program execution.

In this research we are concerned with performing validation using runtime monitors based on a subset of Duration Calculus. Duration Calculus is an Interval Temporal Logic that applies the Reimann integral over properties values to determine their satisfiability. This is possible by considering time over the real numbers. Duration Calculus is highly expressive and its consideration of time as a real number makes it undecidability. Undecidability is surmounted by restricting Duration Calculus notation to its discrete and deterministic subset.

The runtime monitors presented in the dissertation require a library that provides a platform for evaluation. The platform proposed is based on the synchronous data-flow programming language Lustre. Lustre endows the runtime monitors with the capacity of predetermining the real memory and time requirements to evaluate properties. Therefore, runtime monitors are not only suitable for real-time applications due to the mathematical notation but endow the user to predetermine the impacts of the system over the actual system implementation.

### 1.1 Objectives

Time dependent behaviour is best captured using temporal logics. The purpose of this dissertation is to study the use of Duration Calculus, an interval temporal logic, as a runtime monitor for capturing the correctness of system behaviour. Temporal logics can specify time in both abstract and real-time notation. Abstract notation hides the clock time dimension and gives a means of abstract measure, like clock cycles. Real-time notation provides a means of clock time measurement, say five seconds. Real-time specification is very difficult to handle because one has to take into consideration the temporal side-effects of introducing a monitoring system. Thus, for the purpose of this study the validation engine is designed to handle only abstract description of time.

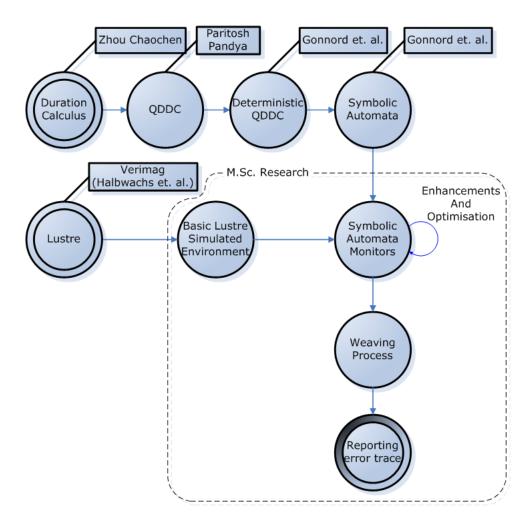

General Duration Calculus is undecidable and thus requires to be restricted to a decidability subset. This dissertation uses the set named as Quantified Discrete-Time Duration Calculus (QDDC) [Pan00] as the decidable subset of Duration Calculus.

Gonnord *et al* [GHR04] showed that QDDC requires the use of non-deterministic automata. The evaluation of non-deterministic automata requires the tracing of different paths at non-deterministic branches as to determine the system correctness. As a direct result the system requirements increase drastically. For the purpose of this dissertation, deterministic automata are preferred as to predetermine the resource requirements of monitors. Endorsing the work of Gonnord *et al*, the dissertation concentrates on defining a suitable deterministic subset for the monitoring system.

The objectives of the dissertation are summarised below:

- 1. to identify the discrete and deterministic subset of duration calculus (based on the work done by Gonnord *et al* [GHR04]);

- 2. define a validation engine for the discrete and deterministic subset of duration calculus using Lustre as a platform;

- 3. propose a generic and platform independent framework for integrating the validation engine inside the system code; and

- 4. analyse the outcome to propose suitable enhancements for the validation engine in general.

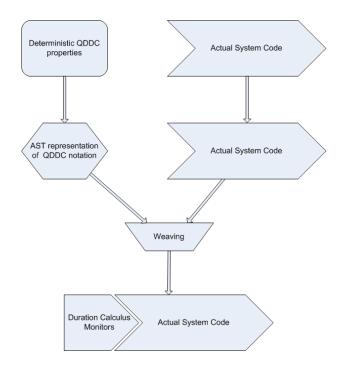

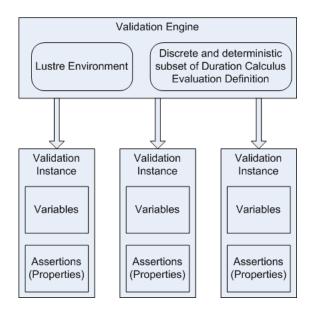

Figure 1.2 provides an overview of how the dissertation combines the discrete and deterministic subset of duration calculus and Lustre to provide the monitoring solution.

An extended objective of the dissertation is to propose the concept of *Interval Temporal Logic-based validation as an aspect* in terms of the new arising concept of Aspect-Oriented

Figure 1.2: Overview diagram of dissertation work.

Programming. This concept frees the design of validation from the complexities involved in the weaving of monitors.

### 1.2 Report Layout

The dissertation consists of three parts – Background, Discrete and Deterministic subset of Duration Calculus Assertions, and Validation and Aspect-Oriented Programming.

The first part consists in providing the necessary background and a review of related projects. The logic notations, both Duration Calculus (DC) and Quantified Discrete Duration Calculus (QDDC), are defined in terms of Church's lambda calculus, as it provides fundamental relations to practical computing [Pen99]. The literature review introduces the traditional assertion as basic monitoring systems. The chapter continues by reviewing related projects while comparing their approach with our solution. The chapter concludes by fitting the proposed real-time monitoring in the Monitoring-Oriented Programming (MoP) concept.

Part II is the dissertation contribution to the Interval Temporal Logic validation area. Chapter 4 proposes a monitoring restricted logic based on QDDC together with both mathematical and execution semantics. The execution semantics of the logic are then used in Chapter 5 to perform state-by-state validation. The chapter also details the design of a validation engine to monitor systems using a Lustre simulated environment. The second part ends by illustrating two validation engine prototypes. The power of the monitoring system and easiness to use in prototyping is founded by two case studies – a mine pump and an answering machine – as depicted in Chapter 7.

The last part of the report shows how validation is an aspect and how Aspect-Oriented Programming (AOP) tools can be used to weave the monitoring system with a program.

# Part I

# Background

### Chapter 2

## **Duration Calculus**

Duration Calculus is a formal notation introduced by Chaochen *et. al.* [CHR91]. Duration Calculus is based on Interval Temporal Logic (ITL) by Moszkowski [Jos01], thus its notation removes the necessity of quantifying and explicitly mentioning time in the formulae. As with ITL, Duration Calculus uses intervals to determine property satisfaction, which is determined by applying the Reimann's integral over the property truth-time values.

In this chapter we introduce the Duration Calculus notation using Church's lambda calculus  $(\lambda$ -calculus).  $\lambda$ -calculus is adopted as it provides good understanding of how the Duration Calculus notation is evaluated and it simplifies the mapping from mathematical notation to implementation.

The high expressiveness of Duration Calculus leads the notation to be undecidable. In order to define a runtime Duration Calculus monitoring system the second section of this chapter restricts the notation to discrete-time, based on the work done by Pandya [Pan00].

### 2.1 Duration Calculus Syntax and Semantics

A number of Interval Temporal Logic notations exist [BMN00, Pet99] but they share a common drawback – the fact that time is considered as a discrete variable. In reality, time is continuous and using the notations mentioned before may lead to some system state loss. On the contrary, Duration Calculus models time and behaviour over the real number line [Jos01, CHR91, Rav94]. This is possible through the use of Reimann's integral as a measure of satisfiability over time.

**Definition 2.1.** (*Time.*) Time is a real valued variable that indicates an instance in the system's life-cycle.

$$\mathbb{T}$$

ime  $\stackrel{df}{=} \mathbb{R}$

Verifying systems throughout their entire life-time is very difficult especially if they do not have any terminating condition. To surmount this problem time is divided into a number of sections referred to as intervals. The following are some important definitions and lemmas that relate to intervals. The interval definitions are later used to define the notation of Duration Calculus.

Definition 2.2. (Set of intervals.) The collection of possible divisions of a system timeline.

$$Intv \stackrel{dy}{=} \{ [b, e] \mid b, e \in \mathbb{T} \cdot b \leqslant e \}$$

For simplification, the boundaries defining the interval are indicated by subscripts b and e. Subscript b represents the start boundary and subscript e represents the end boundary. For example, given any interval,  $\mathcal{I}$ ,  $\mathcal{I}_b$  denotes the interval start point and  $\mathcal{I}_e$  the end point of the same interval. Formally, for any interval [s, f],

$$[s, f]_b \stackrel{df}{=} s$$

$$[s, f]_e \stackrel{df}{=} f$$

**Lemma 2.3.** (Set of point intervals.) Let  $\mathcal{I}$  be an interval. Then the set of intervals consisting of a single point is given by:

Intv<sub>0</sub>

$$\stackrel{df}{=} \{ \mathcal{I} \mid \mathcal{I}_b = \mathcal{I}_e \}$$

It must be noted that  $Intv_0 \subset Intv$ .

**Definition 2.4.** *(Length of interval.)* Time is modelled as a real number. Therefore, the difference between the start and end points of an interval denotes the length of interval.

$$\#(\mathcal{I}) \stackrel{df}{=} \mathcal{I}_e - \mathcal{I}_b$$

**Definition 2.5.** (*Interval meeting.*) Two intervals are said to meet, or consecutive, if and only if the end point of the first interval and starting point of the second interval are the same.

$$\mathcal{I}; \mathcal{J} \stackrel{df}{=} \mathcal{I} \cup \mathcal{J}$$

provided that  $\mathcal{I}_e = \mathcal{J}_b$

**Definition 2.6.** (*State variables.*) A state variable is an atomic boolean variable whose truth varies over time.

state variable

$$\in \mathbb{T} \mapsto \mathbb{B}$$

Definition 2.7. (True.) The state variable true returns true irrespective of time.

$$\mathbb{1} \stackrel{df}{=} \lambda t : \mathbb{T} \cdot true$$

Likewise,

Definition 2.8. (False.) The state variable false returns false irrespective of time.

$$\emptyset \stackrel{df}{=} \lambda t : \mathbb{T} \cdot \boldsymbol{false}$$

**Definition 2.9.** (*State expressions.*) Expressions consisting of logic operators applied to state variables.

For any state variables P and Q

$$\neg P \stackrel{\text{df}}{=} \lambda t : \mathbb{T} \cdot \neg P(t)$$

$$(P \lor Q) \stackrel{\text{df}}{=} \lambda t : \mathbb{T} \cdot P(t) \lor Q(t)$$

$$(P \land Q) \stackrel{\text{df}}{=} \lambda t : \mathbb{T} \cdot P(t) \land Q(t)$$

$$(P \Rightarrow Q) \stackrel{\text{df}}{=} \lambda t : \mathbb{T} \cdot P(t) \Rightarrow Q(t)$$

$$(P \Leftrightarrow Q) \stackrel{\text{df}}{=} \lambda t : \mathbb{T} \cdot P(t) \Leftrightarrow Q(t)$$

**Definition 2.10.** (Duration formula.) A duration formula is a mapping of state expressions evaluated over an interval to boolean values.

Duration formula  $\in$  Intv $\mapsto$  B

Duration Calculus definitions are now introduced based on the definitions given above. An important assumption considered here is that variables have finite variability in a finite interval. In other words, a variable can change its truth value for a finite number of times over finite intervals. This assumption aids in avoiding the Zeno's dichotomy paradox [Wei05].

**Definition 2.11.** (Duration.) The duration of a state expression P in an observation interval  $\mathcal{I} \in Intv$  is obtained by calculating the area under the behaviour-time graph covered by the interval. In mathematics the area is obtained by taking the Reimann boundary integral of the curve. Therefore,

$$\int P = n \stackrel{df}{=} \lambda \mathcal{I} : Intv \cdot \int_{t \in \mathcal{I}} P(t) \, dt = n$$

**Definition 2.12.** (Duration expressions.) Duration expressions consists of duration formulae bound with basic logic operators. For any duration formulae D and F

For any duration formulae D and E

$$\neg D \stackrel{df}{=} \lambda \mathcal{I} : Intv \cdot \neg D(\mathcal{I})$$

$$D \lor E \stackrel{df}{=} \lambda \mathcal{I} : Intv \cdot D(\mathcal{I}) \lor E(\mathcal{I})$$

$$D \land E \stackrel{df}{=} \lambda \mathcal{I} : Intv \cdot D(\mathcal{I}) \land E(\mathcal{I})$$

$$D \Rightarrow E \stackrel{df}{=} \lambda \mathcal{I} : Intv \cdot D(\mathcal{I}) \Rightarrow E(\mathcal{I})$$

$$D \Leftrightarrow E \stackrel{df}{=} \lambda \mathcal{I} : Intv \cdot D(\mathcal{I}) \Leftrightarrow E(\mathcal{I})$$

**Definition 2.13.** (*Chop.*) The chop operator is an arbitrary interval divisor where the left duration formula holds in the first subinterval and the right duration formula in the remaining interval.

For any D and E duration formulas

$$D^{\widehat{}}E \stackrel{df}{=} \lambda \mathcal{I} : Intv \cdot \exists \mathcal{J}, \mathcal{K} : Intv \cdot \mathcal{I} = \mathcal{J}; \mathcal{K} \wedge D(\mathcal{J}) \wedge E(\mathcal{K})$$

Using the definitons above a number of duration operators can be introduced.

**Definition 2.14.** (Not of duration equal to.) The duration of a state expression P in an observation interval  $\mathcal{I} \in Intv$  is not equal to a constant.

$$\int P \neq n \stackrel{df}{=} \neg \left(\int P = n\right)$$

**Definition 2.15.** (Duration of at least.) In an observation interval  $\mathcal{I} \in Intv$  the duration of state expression P is at least of n units.

$$\int P \ge n \stackrel{df}{=} \left(\int P = n\right) \widehat{\mathbf{true}}$$

**Definition 2.16.** (Of greater duration than.) A state expression P has a duration greater than a constant value.

$$\int P > n \stackrel{df}{=} \left( \int P \ge n \right) \land \left( \int P \ne n \right)$$

Endowed with the above formulae the comparison operators are lifted to compare duration formulae.

**Definition 2.17.** (Duration equality.) Two state variables are of equal duration if their duration value is identical for the same interval.

$$\int P = \int Q \stackrel{dj}{=} \lambda \mathcal{I} : Intv \cdot \exists n : \mathbb{R}^+ \cdot (\int P = n) \land (\int Q = n)$$

10

**Definition 2.18.** (Duration  $\neq$ .) Two state variables are said to be of non-equal duration if their duration are of different length for the same observational interval.

$$\int P \neq \int Q \stackrel{df}{=} \neg \left(\int P = \int Q\right)$$

**Definition 2.19.** (Duration  $\geq$ .) A duration of a state variable is greater than or equal to another state variable's duration if for the same interval, the number of truths of the first state variable is at least equal to the number of truths of the second state variable.

$$\int P \ge \int Q \stackrel{df}{=} (\int P = \int Q)^{\uparrow} true$$

**Definition 2.20.** (Duration >.) A duration of a state variable is greater than another's state variable duration if and only if for the same interval the first state variable evaluates to true more frequently than the second state variable.

$$\int P > \int Q \stackrel{df}{=} \left( \int P \ge \int Q \right) \land \left( \int P \neq \int Q \right)$$

Other comparison operators can be defined in a similar way.

**Theorem 2.21.** (Duration of true.) A tautological state variable is equal to the length of the observational interval.

$$\left(\int \mathbb{1} = n\right)(\mathcal{I}) \iff \#(\mathcal{I}) = n$$

*Proof.* The proof is obtained directly from Definitions 2.11 and 2.4.

$$\begin{pmatrix} \int \mathbb{1} = n \end{pmatrix} (\mathcal{I}) \stackrel{df}{=} \int_{t \in \mathcal{I}} \mathbb{1}(t) dt = n \quad \text{Definition 2.11.} \\ = [t]_{\mathcal{I}} = n \quad \text{Evaluation of integral.} \\ = \mathcal{I}_e - \mathcal{I}_b = n \quad \text{Expanding integral result.} \\ = \#(\mathcal{I}) = n \quad \text{Definition 2.4.}$$

To simplify the reading of duration formulae, len will be used interchangeably with  $\int \mathbb{1}$ .

$$len \stackrel{df}{=} \int 1$$

**Corollary 2.22.** (Upper duration limit.) The duration of a state variable P can reach its maximum value if and only if it is a tautology within the interval.

$$\int P \leqslant \int \mathbb{1}$$

**Lemma 2.23.** (Duration of a negated state variable.) For any state variable P the duration of P's complement within an interval is equal to the length of the interval less the duration of P.

$$\left(\int \neg P = n\right) = \left(\int \mathbb{1} - \int P = n\right)$$

**Theorem 2.24.** (Duration of false.) A contradictory state variable is equal to the constant function zero.

$$\int 0(\mathcal{I}) = 0$$

*Proof.* The proof is again obtained directly from Definition 2.11.

$$\begin{aligned} \int \mathfrak{O}(\mathcal{I}) &= \int_{t \in \mathcal{I}} \mathfrak{O}(t) \, dt & \text{Definition 2.11.} \\ &= [\mathfrak{O}t]_{\mathcal{I}} & \text{Evaluation of integral.} \\ &= 0 & \text{Expanding integral result.} \end{aligned}$$

**Corollary 2.25.** (Lower duration limit.) The duration of a state variable P can reach its least value if and only if it is a contradiction within the observation interval.

$$\int P \ge \int 0$$

**Theorem 2.26.** (Addition of durations.) The combined duration of two state variables is the sum of the values where either P or Q is true together with the values where both are satisfied simultaneously.

For any state variables P and Q

$$\int P + \int Q = \int (P \lor Q) + \int (P \land Q)$$

As with any logic-based models, state variables are not enough to describe all the features and properties within a system. To extend the expressiveness of Duration Calculus, state variables are lifted to predicates as in interval temporal logic [CHR91].

**Definition 2.27.** (Almost everywhere true predicate.) A state formula P is true for the entire non-point intervals.

$$\left\lceil P \right\rceil \stackrel{df}{=} \left( \int P = \int \mathbb{1} \right) \land \left( len > 0 \right)$$

10

**Definition 2.28.** (*Point interval predicate.*) A predicate that is true only for a point interval is denoted by [].

$$\left[ \ \right] \stackrel{df}{=} len = 0$$

**Definition 2.29.** (*True predicate.*) When a predicate holds for both continuous and point intervals it is said to be a tautological predicate.

$$tt \stackrel{df}{=} len \ge 0$$

Theorem 2.30. (Predicate implication.) Given a predicate P

$$\begin{bmatrix} P \end{bmatrix} \Rightarrow \int \neg P = 0 \\ \begin{bmatrix} \rceil \end{bmatrix} \Rightarrow \int P = 0$$

**Theorem 2.31.** (Duration monotonicity.) For any states P and Q if  $P \Rightarrow Q$  then the duration of P must be less or equal to that of Q.

$$\lceil P \Rightarrow Q \rceil \Rightarrow (\int P \le \int Q)$$

*Proof.* The order preservation in duration formula is conserved through the duration notation semantics.

$$\begin{array}{ll} \lceil P \Rightarrow Q \rceil \Rightarrow \lceil \neg P \lor Q \rceil & \text{Implication equivalence} \\ \Rightarrow \left( \int (\neg P \lor Q) = \int \mathbb{1} \right) \land \left( \int \mathbb{1} > 0 \right) & \text{Definition 2.27} \\ \Rightarrow \int (\neg P) + \int Q - \int (\neg P \land Q) = \int \mathbb{1} & \text{Theorem 2.26} \\ \Rightarrow \int \mathbb{1} - \int P + \int Q - \int (\neg P \land Q) - \int \mathbb{1} = 0 & \text{Theorem 2.23} \\ \Rightarrow \int P = \int Q - \int (\neg P \land Q) & \text{Basic algebra} \\ \Rightarrow \int P \leq \int Q & \text{For some } \int X \ge 0 \end{array}$$

Using the definition of chop, the two basic time operators of modal logic can be defined as follows.

**Definition 2.32.** (*Eventually.*) A duration formula D is said to become true if there is a subinterval where it evaluates to true.

$$\Diamond D \stackrel{df}{=} tt^D tt$$

**Definition 2.33.** (Always.) A duration formula D is always true if it holds over all subintervals within the observation interval.

$$\Box D \stackrel{df}{=} \neg \diamondsuit \neg D$$

**Theorem 2.34.** (Duration in subintervals.) The duration of a state in an interval is the duration of the state in each subinterval.

Given a state formula P and an interval divided into two subintervals of length r and s respectively.

$$(\int P = r + s) \Leftrightarrow (\int P = r)^{\wedge} (\int P = s)$$

### **Duration Calculus syntax**

| $<$ state variable $> \in$                                                                                                                                                                                                                                     | $\mathbb{T}\mapsto \mathbb{B}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $<$ natural number $> = \frac{df}{df}$                                                                                                                                                                                                                         | $\mathbb{N}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <state expression=""> ::=  <br/> <br/> <br/> <br/> </state>                                                                                                                                                                                                    | <state variable><br>$<$ state expression> $\lor$ $<$ state expression><br>$<$ state expression> $\land$ $<$ state expression><br>$<$ state expression> $\Rightarrow$ $<$ state expression><br>$<$ state expression> $\Leftrightarrow$ $<$ state expression><br>$\neg$ $<$ state expression>                                                                                                                                                                                                                                                                                                                                                                                       |

| $\begin{vmatrix} & \int & \cdot \\ & & \int & \cdot \\ & & \int & \cdot \\ & & & & \int & \cdot \\ & & & & & \langle & \circ \\ & & & & \circ & \circ \\ & & & & & \circ & \circ \\ & & & &$ | <pre><state expression="">=&lt; natural number &gt; <state expression="">&gt; &lt; natural number &gt; <state expression="">= <math>\int &lt;</math>state expression &gt; <state expression="">&gt; <math>\int &lt;</math>state expression &gt;&gt; <state expression="">] d.c. formula &gt; <math>\land &lt;</math>d.c. formula &gt; d.c. formula &gt; <math>\lor &lt;</math>d.c. formula &gt; d.c. formula &gt; <math>\Leftrightarrow &lt;</math>d.c. formula &gt; d.c. formula &gt; <math>\Leftrightarrow &lt;</math>d.c. formula &gt; &lt;<d.c. formula=""> &lt;<d.c. formula=""> </d.c.>) &lt;<d.c. formula="">)</d.c.></d.c.></state></state></state></state></state></pre> |

#### 2.1.1 Duration Calculus examples

Consider a simple property stating that over a given interval a loop will not exceed the 30 seconds run in total. The property is represented in Duration Calculus as,

$$\int loop \leq 30 \, seconds$$

A less rigid control over the loop can be specified as,

$$\Box ([loop] \Rightarrow len \leq 30 \, seconds)$$

The latter formula states that the loop can be executed several times given that every execution never exceeds 30 seconds. On the contrary, the earlier version allows the loop to enter and exit its body for a number of times given that the total execution time does not exceed the 30 seconds interval.